- 您现在的位置:买卖IC网 > Sheet目录382 > 450-0037 (LS Research LLC)MODULE TIWI-R2 U.FL

TiWi-R2 TRANSCEIVER MODULE

DATASHEET

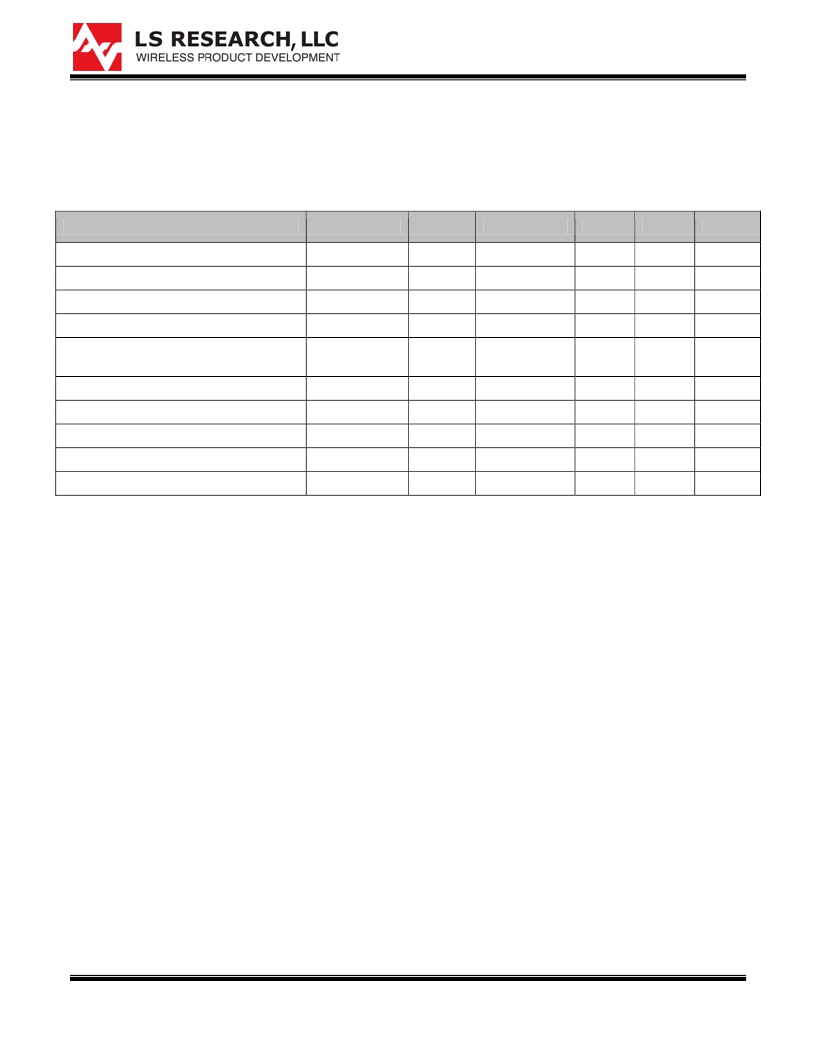

SLOW (32 KHZ) CLOCK SOURCE REQUIREMENTS

The slow clock is always supplied from an external source. It is input on the SLOW_CLK pin, and can be a digital

signal in the range of VIO only. For slow clock frequency and accuracy refer to Table 14. The external slow clock

must be stable before the system exits from shut down mode.

Parameter [1]

Condition

Symbol

Min

Typ

Max

Unit

Input slow clock frequency

32768

Hz

Input slow clock accuracy

Input transition time T r /T f – 10% to 90%

WLAN, BT

T r /T f

+/-250

100

ppm

ns

Frequency input duty cycle

30

50

70

%

Input voltage limits

Square wave,

DC coupled

VIH

0.65 x VDDS

VDDS

V peak

VIL

0

0.35 x VDDS

Input impedance

Input capacitance

Rise and fall time

1

5

100

MW

pF

ns

Phase noise

1 kHz

-125

dBc/Hz

[1] Slow clock is a fail safe input

Table 14 Slow Clock Source Requirements

The information in this document is subject to change without notice.

330-0045-R4.0

Copyright ? 2010-2012 LS Research, LLC

Page 21 of 41

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

450-0085

COM6L-T5 ADAPTER CARD WITH U.FL

450-0089

EVAL MODULE TIWI-SL

4515-DS5A020DP

SENSOR DIFF PRESS 20H20 8DIP PCB

4515DO-DS5AI020DP

SENSOR DIFF PRESS 20H20 8DIP PCB

4525-DS5A001DP

SENSOR DIFF PRESS 1PSI 8DIP PCB

4525DO-DS5AI030DP

SENSOR DIFF PRESS 30PSI 8DIP PCB

456

LAMP INCAND G4-1/2 MINI BAYONET

459

LAMP INCAND 5MM MIDG FLANGE 22V

相关代理商/技术参数

450-0037R

功能描述:WiFi/802.11模块 TiWi-R2 Module, U.FL Conn, Tape and Reel

RoHS:否 制造商:Taiyo Yuden 支持协议:802.11 b/g/n 频带: 数据速率:150 Mbps 接口类型:SDIO 传输功率(最大): 天线连接器类型: 工作电源电压:3.4 V to 5.5 V 传输供电电流: 接收供电电流: 最大工作温度:+ 80 C 尺寸:35 mm x 15 mm x 2.9 mm

450-003A

制造商:LG Corporation 功能描述:ADAPTER ANT (75/300) *CONTAINE

450-003B

制造商:LG Corporation 功能描述:ADAPTOR ANT

45-0003-BK

制造商:DATACOMM ELECTRONICS 功能描述:CABLE PASS THROUGH WALL PLATE RECESSED IN WALL LT BLACK

45-0003-WH

制造商:DATACOMM ELECTRONICS 功能描述:CABLE PASS THROUGH WALL PLATE RECESSED IN WALL WHITE

450004083880002

功能描述:工业移动感应器和位置传感器 RESISTIVE & OPTICAL RoHS:否 制造商:Honeywell 输出类型:Analog - Current 电压额定值:12 VDC to 30 VDC 线性:+/- 0.0011 % 温度范围:- 40 C to + 85 C 总电阻: 容差: 类型:Rotary Sensor

450-0047

功能描述:Zigbee/802.15.4模块 SiFLEX02-HP U.fl Module

RoHS:否 制造商:Digi International 频带:902 MHz to 928 MHz 视线范围: 数据速率: 灵敏度: 工作电源电压:2.4 V to 3.6 V 传输供电电流:215 mA 接收供电电流:26 mA 输出功率:250 mW 天线连接器类型:Wire 最大工作温度:+ 85 C 尺寸:32.94 mm x 22 mm x 2.03 mm

450-0049

功能描述:Zigbee/802.15.4模块 SiFLEX02-HP RF Castellation Module, RoHS RoHS:否 制造商:Digi International 频带:902 MHz to 928 MHz 视线范围: 数据速率: 灵敏度: 工作电源电压:2.4 V to 3.6 V 传输供电电流:215 mA 接收供电电流:26 mA 输出功率:250 mW 天线连接器类型:Wire 最大工作温度:+ 85 C 尺寸:32.94 mm x 22 mm x 2.03 mm